Chapter 5: Difference between revisions

Jump to navigation

Jump to search

| (52 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

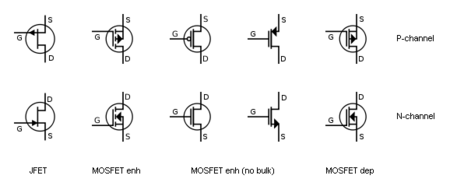

===Metal-oxide semiconductor field effect transistor (MOSFET) === |

===Metal-oxide semiconductor field effect transistor (MOSFET) === |

||

[[Image:Mosfet.PNG|thumb|450px|Circuit symbols for various FETs]] |

[[Image:Mosfet.PNG|thumb|450px|Circuit symbols for various FETs]] |

||

| ⚫ | |||

| ⚫ | |||

| ⚫ | |||

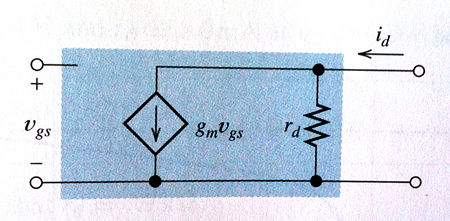

[[Image:IMG_0293.JPG|thumb|450px|FET small-signal equivalent circuit ]] |

|||

[[Image:Common-Gate_FET.png|thumb|450px|Common-Gate FET]] |

|||

"The FET controls the flow of electrons (or electron holes) from the source to drain by affecting the size and shape of a "conductive channel" created and influenced by voltage (or lack of voltage) applied across the gate and source terminals (For ease of discussion, this assumes body and source are connected). This conductive channel is the "stream" through which electrons flow from source to drain."<ref>Wikipedia: Field-effect transistor http://en.wikipedia.org/wiki/Field-effect_transistor</ref> |

"The FET controls the flow of electrons (or electron holes) from the source to drain by affecting the size and shape of a "conductive channel" created and influenced by voltage (or lack of voltage) applied across the gate and source terminals (For ease of discussion, this assumes body and source are connected). This conductive channel is the "stream" through which electrons flow from source to drain."<ref>Wikipedia: Field-effect transistor http://en.wikipedia.org/wiki/Field-effect_transistor</ref> |

||

*'''Enhancement''': The electric field from the gate voltage forms an induced channel allowing current to flow. |

*'''Enhancement''': The electric field from the gate voltage forms an induced channel allowing current to flow. |

||

*'''Depletion''': The channel is physically implanted rather than induced |

*'''Depletion''': The channel is physically implanted rather than induced. |

||

*'''JFET''': Charge flows through a semiconducting channel (between the source and drain). Applying a bias voltage to the gate terminal impedes the current flow (or pinches it off completely) |

*'''JFET''': Charge flows through a semiconducting channel (between the source and drain). Applying a bias voltage to the gate terminal impedes the current flow (or pinches it off completely). |

||

'''''Talk about the irregular pinched off shape of a JFET. Insert a photo.''''' |

|||

===Threshold Voltage=== |

===Threshold Voltage=== |

||

*The threshold voltage, <math>V_{to}</math>, is the minimum <math>v_{GS}</math> needed to move the transistor from the Cutoff to Triode region. |

*The threshold voltage, <math>V_{to}</math>, is the minimum <math>v_{GS}</math> needed to move the transistor from the Cutoff to Triode region. |

||

| ⚫ | |||

{| |

{| |

||

|STYLE="vertical-align: top" | |

|STYLE="vertical-align: top" | |

||

{| class="wikitable" border="1" style="text-align:center" |

{| class="wikitable" border="1" style="text-align:center" |

||

|+'''<math>V_{to}</math> for various FETs''' |

|||

! Type !! n-Channel!! p-Channel |

! Type !! n-Channel!! p-Channel |

||

|- |

|- |

||

| Line 23: | Line 27: | ||

|STYLE="vertical-align: top" | |

|STYLE="vertical-align: top" | |

||

{| |

{| |

||

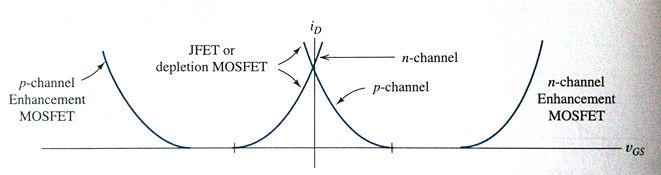

[[Image:IMG_0292.JPG| |

[[Image:IMG_0292.JPG|x175px|none]] |

||

|} |

|} |

||

|} |

|} |

||

===Modes of operation=== |

===Modes of operation=== |

||

| ⚫ | |||

| ⚫ | |||

| ⚫ | |||

*'''Cutoff''' |

*'''Cutoff''' |

||

:*The channel has not been created (Enhancement) or is pinched off (Depletion & JFET). No current flows. |

:*The channel has not been created (Enhancement) or is pinched off (Depletion & JFET). No current flows. |

||

*'''Triode:''' |

*'''Triode:''' |

||

:*When |

:*When <math>v_{GS}=V_{to}</math> is reached, a channel forms beneath the gate (Enhancement) or is no longer pinched off (Depletion & JFET), allowing current to flow. |

||

:*As <math>v_{DS}</math> increases, the voltage between the gate and channel becomes smaller as you progress towards the drain. This results in the channel tapering off as you get closer to the drain. |

|||

| ⚫ | |||

:* |

::*" Because of the tapering of the channel, its resistance becomes larger with increasing <math>v_{DS}</math>, resuling in a lower rate of increase of <math>i_D</math>." <ref>Electronics p. 291</ref> |

||

::*'''Why doesn't it just cut the current off completely when v_DS gets high enough? If it is pinched off, how does the current flow still?''' |

|||

*'''Saturation:''' |

*'''Saturation:''' |

||

:*When <math>v_{DG}=V_{to}</math> is reached, the channel thickness at the drain end becomes zero (Enhancement, Depletion & JFET). |

|||

:*"Now consider what happens if we continue to increase <math>v_{DS}</math>. Because of the current flow, the voltages between points along the channel and the source become greater as we move toward the drain. Thus, the voltage between gate and channel becomes smaller as we move toward the rain, resulting in a tapering of the channel thickness as illustrated in Figure 5.5. Because of the tapering of the channel, its resistance becomes larger with increasing <math>v_{DS}</math>, resuling in a lower rate of increase of <math>i_D</math>." <ref>Electronics p. 291</ref> |

|||

===<math>i_D</math>, <math>V_{to}</math> and PMOS/NMOS=== |

|||

===Device equations=== |

===Device equations=== |

||

{| |

{| |

||

| Line 69: | Line 67: | ||

|} |

|} |

||

|} |

|} |

||

{| |

|||

|STYLE="vertical-align: top" | |

|||

{| class="wikitable" border="1" style="text-align:center" |

{| class="wikitable" border="1" style="text-align:center" |

||

|+ '''Drain current''' |

|+ '''Drain current''' |

||

! Region!! <math>i_D</math> |

! Region!! <math>i_D</math> |

||

|- |

|- |

||

| Cutoff|| <math>0</math> |

|||

| Cutoff|| <math>0</math> || rowspan="4" | <math>\frac{W}{L}\frac{\mu_n C_{ox}}{2}=\frac{W}{L}\frac{KP}{2}</math> || rowspan="4" | <math>\frac{I_{DSS}}{V_{to}^2}</math> |

|||

|- |

|- |

||

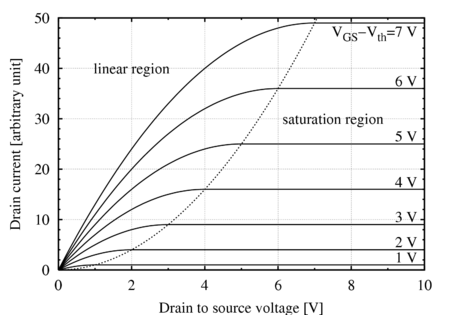

| Triode|| <math>K [2(v_{GS}-V_{to})v_{DS}-v^2_{DS}]</math> |

| Triode|| <math>K [2(v_{GS}-V_{to})v_{DS}-v^2_{DS}]</math> |

||

| Line 82: | Line 81: | ||

| Boundry || <math>Kv^2_{DS}</math> |

| Boundry || <math>Kv^2_{DS}</math> |

||

|} |

|} |

||

|STYLE="vertical-align: top" | |

|||

| ⚫ | |||

|+'''K''' |

|||

!Type !! K |

|||

| ⚫ | |||

|Enhancement <br> Depletion|| <math>\frac{1}{2}\mu_nC_{ox}\frac{W}{L}=\frac{1}{2}KP\frac{W}{L}</math> |

|||

| ⚫ | |||

|JFET || <math>\frac{I_{DSS}}{V_{to}^2}</math> |

|||

| ⚫ | |||

| ⚫ | |||

*Device Parameters: <math>KP=\mu_n C_{ox}</math> |

*Device Parameters: <math>KP=\mu_n C_{ox}</math> |

||

*Surface Mobility: <math>\mu_n</math>, the electrons in the channel |

*Surface Mobility: <math>\mu_n</math>, the electrons in the channel |

||

*Capacitance of the gate per unit area: <math>C_{ox}</math> |

*Capacitance of the gate per unit area: <math>C_{ox}</math> |

||

===Transconductance & Drain Resistance=== |

|||

| ⚫ | |||

*Looking at the FET small-signal equivalent circuit, we can write <math>i_d=g_m v_{gs}+\frac{v_{ds}}{r_d}</math>, thus <math>g_m=\frac{i_d}{v_{gs}} \bigg|_{v_{ds}=0}</math>. Since these are small changes from the Q-point, we can write <math>g_m=\frac{\partial i_D}{\partial v_{GS}}\bigg|_{Q-point}</math>. Similarly, we can write <math>\frac{1}{r_d}=\frac{\partial i_D}{\partial v_{DS}}\bigg|_{Q-point}</math> |

|||

*<math>g_m=\frac{\partial i_D}{\partial v_{GS}}\bigg|_{Q-point}</math> |

|||

*<math>\frac{1}{r_d}=\frac{\partial i_D}{\partial v_{DS}}\bigg|_{Q-point}</math> |

|||

=== |

===Small-signal analysis=== |

||

| ⚫ | |||

| ⚫ | |||

| ⚫ | |||

| ⚫ | |||

| ⚫ | |||

| ⚫ | |||

| ⚫ | |||

| BJT || || |

|||

| ⚫ | |||

===Analysis=== |

|||

#Analyze the DC circuit to find the Q-point (using nonlinear device equations or characteristic curves) |

#Analyze the DC circuit to find the Q-point (using nonlinear device equations or characteristic curves) |

||

#Use the small-signal equivalent circuit to find the impedance and gains |

#Use the small-signal equivalent circuit to find the impedance and gains |

||

===Small-signal equivalent circuits=== |

|||

'''''Insert photo''''' |

|||

| ⚫ | |||

*Transconductance is defined as <math>g_m=2K(V_{GSQ}-V_{to})=\sqrt {2KP} \sqrt {W/L} \sqrt{I_{DQ}}</math>. |

|||

:*<math>i_d=g_mv_{gs}+\frac{v_{ds}}{r_d}</math>, where r<sub>d</sub> is the drain resistance |

|||

{| class="wikitable" border="1" align="center" |

{| class="wikitable" border="1" align="center" |

||

|+ |

|+ |

||

! Type!! Voltage Gain || Current Gain || Power Gain ||Input Impedance || Output Impedance|| Frequency Response |

! Type!! Voltage Gain || Current Gain || Power Gain ||Input Impedance || Output Impedance|| Frequency Response || Comments |

||

|-align="center" |

|-align="center" |

||

| Common-Source|| |

| Common-Source||<math>A_v>-1</math> || <math>A_i>-1</math> || <math>G > 1</math> || High || Low || ||Using <math>A_i=A_v*\frac{R_{in}}{R_L}</math>. '''Can you really have such a large voltage *and* current gain?''' |

||

|-align="center" |

|-align="center" |

||

| Source Follower|| || || || |

| Common-Drain<br>Source Follower|| <math>A_v<1</math>|| <math>A_i>1</math>|| <math>G>1</math> ||High || Low || || |

||

|-align="center" |

|-align="center" |

||

| Common-Gate || <math>\frac{g_mR_sr_dR_DR_L}{(R_DR_L+r_dR_L+r_dR_D)(R_i+R_S)}</math> || || || || || || http://users.ece.gatech.edu/mleach/ece3050/notes/mosfet/cgamp.pdf |

|||

| Common-Gate || || || || |

|||

|} |

|} |

||

===MOSFET vs JFET vs BJT=== |

|||

{| class="wikitable" border="1" |

|||

| ⚫ | |||

|- |

|||

| ⚫ | |||

|- |

|||

| ⚫ | |||

|- |

|||

| BJT || Current-controlled current source|| |

|||

|} |

|||

===Questions=== |

===Questions=== |

||

*How do you find r<sub>d</sub>? |

*How do you find r<sub>d</sub>? |

||

| Line 126: | Line 129: | ||

*CMOS nand/nor gates |

*CMOS nand/nor gates |

||

*JFET only goes to I<sub>DSS</sub>? |

*JFET only goes to I<sub>DSS</sub>? |

||

===References=== |

===References=== |

||

<references/> |

<references/> |

||

Latest revision as of 13:58, 22 March 2010

Metal-oxide semiconductor field effect transistor (MOSFET)

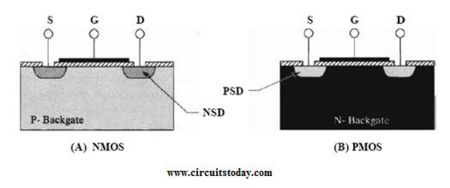

"The FET controls the flow of electrons (or electron holes) from the source to drain by affecting the size and shape of a "conductive channel" created and influenced by voltage (or lack of voltage) applied across the gate and source terminals (For ease of discussion, this assumes body and source are connected). This conductive channel is the "stream" through which electrons flow from source to drain."<ref>Wikipedia: Field-effect transistor http://en.wikipedia.org/wiki/Field-effect_transistor</ref>

- Enhancement: The electric field from the gate voltage forms an induced channel allowing current to flow.

- Depletion: The channel is physically implanted rather than induced.

- JFET: Charge flows through a semiconducting channel (between the source and drain). Applying a bias voltage to the gate terminal impedes the current flow (or pinches it off completely).

Threshold Voltage

- The threshold voltage, , is the minimum needed to move the transistor from the Cutoff to Triode region.

- is usually on the order of a couple of volts

|

|

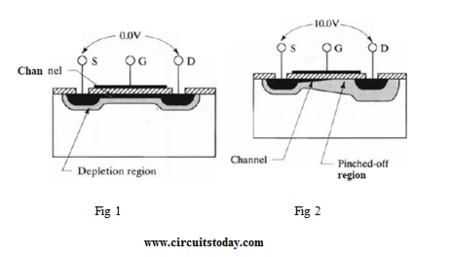

Modes of operation

- Cutoff

- The channel has not been created (Enhancement) or is pinched off (Depletion & JFET). No current flows.

- Triode:

- When is reached, a channel forms beneath the gate (Enhancement) or is no longer pinched off (Depletion & JFET), allowing current to flow.

- As increases, the voltage between the gate and channel becomes smaller as you progress towards the drain. This results in the channel tapering off as you get closer to the drain.

- " Because of the tapering of the channel, its resistance becomes larger with increasing , resuling in a lower rate of increase of ." <ref>Electronics p. 291</ref>

- Why doesn't it just cut the current off completely when v_DS gets high enough? If it is pinched off, how does the current flow still?

- Saturation:

- When is reached, the channel thickness at the drain end becomes zero (Enhancement, Depletion & JFET).

Device equations

|

| |||||||||||||||||||||||||||

|

|

- Device Parameters:

- Surface Mobility: , the electrons in the channel

- Capacitance of the gate per unit area:

Transconductance & Drain Resistance

- "Transconductance, , is an important parameter in the design of amplifier circuits. In general, better performance is obtained with higher values of ." It is obtained at the cost of chip area.<ref>Electroincs p. 310</ref>

- Looking at the FET small-signal equivalent circuit, we can write , thus . Since these are small changes from the Q-point, we can write . Similarly, we can write

Small-signal analysis

- Analyze the DC circuit to find the Q-point (using nonlinear device equations or characteristic curves)

- Use the small-signal equivalent circuit to find the impedance and gains

| Type | Voltage Gain | Current Gain | Power Gain | Input Impedance | Output Impedance | Frequency Response | Comments |

|---|---|---|---|---|---|---|---|

| Common-Source | High | Low | Using . Can you really have such a large voltage *and* current gain? | ||||

| Common-Drain Source Follower |

High | Low | |||||

| Common-Gate | http://users.ece.gatech.edu/mleach/ece3050/notes/mosfet/cgamp.pdf |

MOSFET vs JFET vs BJT

| Transistor | Pros | Cons |

|---|---|---|

| MOSFET | *Draws no gate current *Infinite input resistance *Voltage-controlled current source |

Gate protection needed to prevent static electricity from breaking down the insulation |

| JFET | ||

| BJT | Current-controlled current source |

Questions

- How do you find rd?

- Roughly what are the breakdown voltages for JFETs?

- CMOS nand/nor gates

- JFET only goes to IDSS?

References

<references/>

![{\displaystyle K[2(v_{GS}-V_{to})v_{DS}-v_{DS}^{2}]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/40bb5b0ffa3dcb84c09c7252ed8fc731f03619f2)